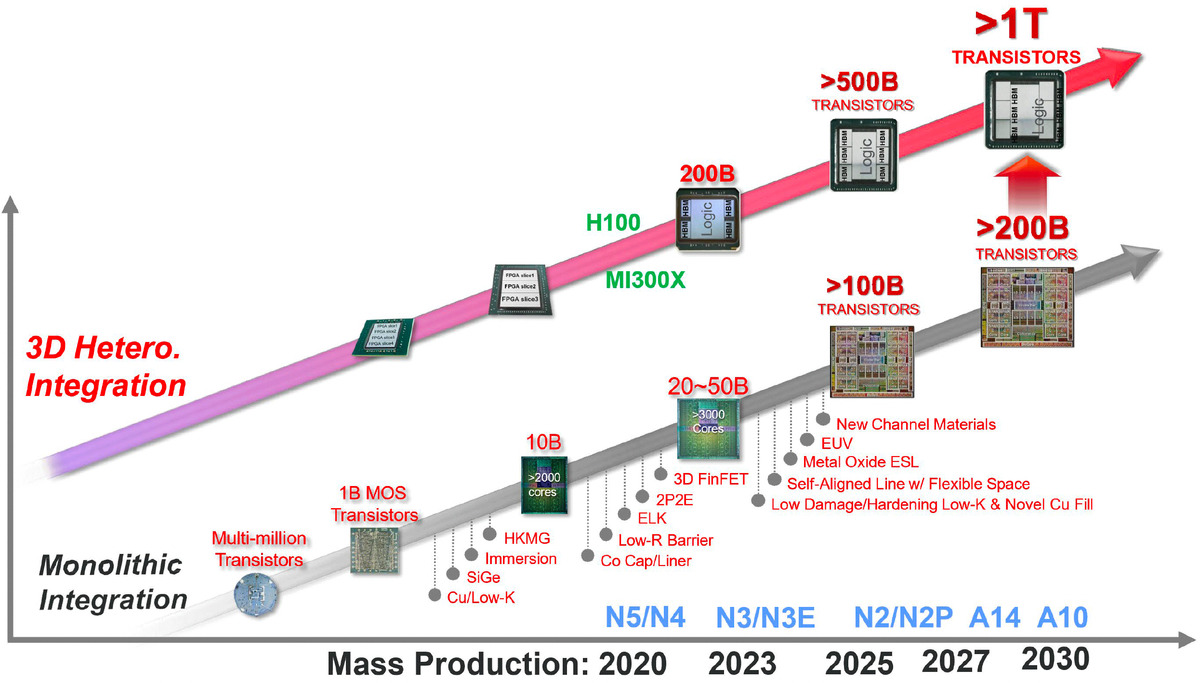

Pada persidangan IEDM (Mesyuarat Peranti Elektron Antarabangsa), TSMC mendedahkan sasaran mereka untuk menyampaikan pakej cip dengan satu trilion transistor.

TSMC juga sedang berusaha untuk membangunkan cip dengan 200 bilion transistor pada sekeping silikon.

Untuk mencapai matlamat itu, TSMC mengesahkan bahawa mereka sedang mengusahakan nod pengeluaran N2 dan N2P kelas 2nm dan proses fabrikasi kelas 1.4nm A14 dan kelas 1nm A10 yang akan tiba menjelang 2030.

Selain itu, TSMC turut melihat kemajuan dalam teknologi pembungkusan (CoWoS, InFO, SoIC, dan lain-lain), yang akan membolehkannya membina penyelesaian berbilang ciplet besar-besaran yang dapat mempakej lebih daripada satu trilion transistor sekitar tahun 2030.

Walaupun perkembangan teknologi proses termaju telah agak perlahan dalam beberapa tahun kebelakangan ini kerana cabaran teknologi dan kewangan, tetapi TSMC yakin akan dapat memajukan nod pengeluarannya dari segi prestasi, kuasa dan ketumpatan transistor dalam tempoh lima atau enam tahun akan datang apabila TSMC melancarkan 2nm, 1.4nm dan nod 1nm.

Ketika ini, cip Nvidia dengan 80 bilion transistor, GH100 ialah salah satu pemproses monolitik yang paling kompleks di pasaran.

Menurut TSMC, mereka akan ada cip monolitik yang lebih kompleks dengan lebih 100 bilion transistor tidak lama lagi.

Tetapi membina pemproses besar seperti itu semakin kompleks dan mahal, jadi banyak syarikat memilih reka bentuk berbilang cip. Sebagai contoh, Instinct MI300X AMD dan Intel Ponte Vecchio yang terdiri daripada berpuluh-puluh ciplet.

{suggest}

Sumber: Toms Hardware, Semi Conductor Engineering